ISSUE: January 2023

## Rad-Hard P-Channel FETs: A Simpler And More-Reliable Solution For Power Distribution In Space

# by Oscar Mansilla, Rushi Patel and Michelle Lozada, International Rectifier HiRel (IR HiRel), an Infineon Technologies Company, El Segundo, Calif.

Overall system reliability remains critical in space applications. This is especially true for the power management and distribution (PMAD) needed to keep the spacecraft operational. With space systems only as strong as their weakest parts, reliability starts at the discrete component level. That includes power MOSFETs, both those used in power converter power stages and those used in power distribution.

For a typical satellite, the mix of power FETs needed is approximately 60% n-channel and 40% p-channel. In this article, we'll discuss the importance of robust safe operating area (SOA) particularly vis-à-vis power applications requiring p-channel FETs, including load switching, load sequencing, redundancy for power sources and loads and inrush current limiting. Then, we'll describe the improvements made in IR HiRel's latest generation of rad hard p-channel MOSFETs, the R9 family of superjunction devices, versus the company's previously introduced R5 family of conventional planar devices, and show the relevance of these improvements in an example inrush current limiting application.

In this article we'll also explore the benefits of p-channel MOSFETs versus n-channel devices in load switching and load sequencing, and touch on the use of p-channel MOSFETs in providing power and load redundancy. Finally, we'll present some measurements taken on IR HiRel's inrush current limiter eval board demonstrating the higher power capability afforded by the R9 devices versus their R5 predecessors.

As we'll see, the wider SOA of the newer devices increases the power handling of the p-channel transistor for a given package size. Moreover, the better R<sub>DS(ON)</sub> performance of these devices may allow some power distribution applications to move away from use of n-channel MOSFETS and take advantage of the simpler gate drive requirements of p-channel MOSFETs.

### Why SOA Matters

The SOA represents the maximum time-dependent voltage and current operating limits that a FET can handle without permanent damage or degradation. This is a key design consideration especially for applications that tend to operate in linear mode such as:

- Protection circuits including

- $\circ$  input undervoltage protection and output overvoltage protection

- short-circuit protection and

- output turn-off discharge

- Pass elements for linear regulators

- Control circuits including output sequencing, hot-swap and soft start.

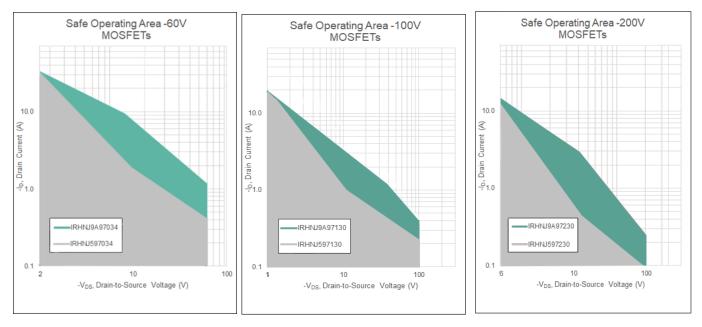

Fig. 1 shows the SOA improvement of the latest-generation rad-hard p-channel devices from IR HiRel. Each plot holds device type and SMD-0.5 package constant with the only variable being device technology, legacy R5 versus latest generation, R9. In all three examples, for 60 V, 100 V and 200 V, the R9 devices significantly expand the envelope for dc SOA.

Fig. 1. IR HiRel's R9 p-channel MOSFETs expand the envelope for dc safe operating area when compared with the company's legacy R5 devices. Three voltage classes of R9 and R5 MOSFETs are compared here.

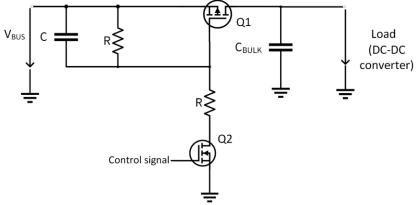

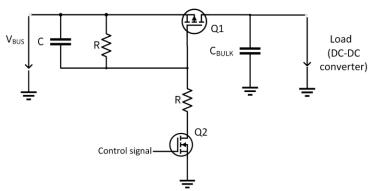

Consider as a typical use case, a 28-V bus connected to bulk capacitors ( $C_{BULK}$ ) at the front end of a dc-dc converter, shown as the load in Fig. 2. If the bus voltage is directly connected to the bulk capacitors during startup, this creates large inrush current spikes, which are unwanted and can affect line regulation.

In this case, we use a transistor  $(Q_1)$  for controlled turn-on that curbs the peak inrush current. If this is not implemented, it may affect bus voltage regulation that can trigger undervoltage lockout (UVLO) of the downstream circuit. Since the satellite bus is also current limited, tight voltage regulation becomes necessary. Such abrupt current spikes can also cause momentary EMI issues which is another reason why it is important to have inrush current limiting capability in power distribution circuits.

Fig. 2. Typical implementation of inrush current limiter.

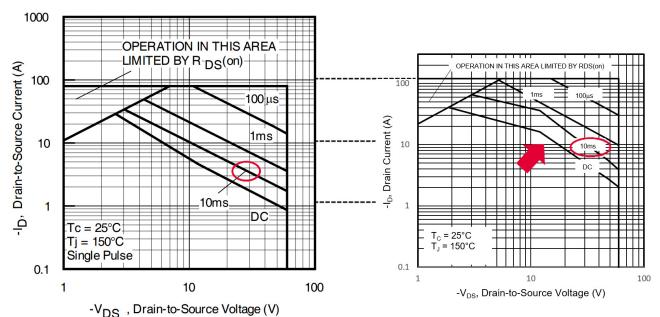

Fig. 3 compares the SOA performance of two devices, R5 and R9 p-channel FETs with the same die size and in the same package, again the only difference being device technology. On the left is the R5 60-V p-channel MOSFET SOA that shows for 10-ms linear mode operation, the max drain current should be no more than about 3.75 A at 28-V for safe operation. On the right is the R9 60-V p-channel MOSFET SOA that shows for the same

voltage and duration, the drain current can be up to 10 A, which is a 250% increase versus the prior R5 generation FET.

*Fig. 3. Comparing the SOA of an R5 60-V p-channel MOSFET (IRHYS597034CM on left) with that of an R9 60-V p-channel MOSFET (IRHYS9A97034CM on right).*

The R9 device has 250% higher current capability.

## Simplified Board Design With P-Channel Devices

### Load Switching

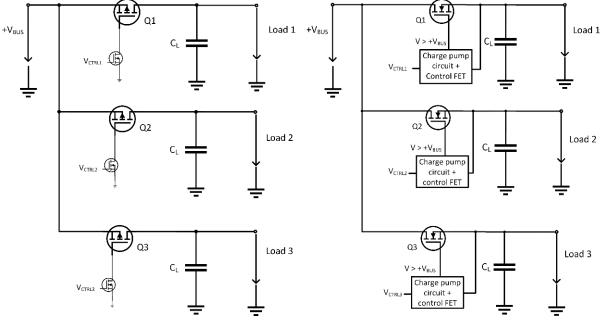

Load switching applications often use p-channel FETs as shown in Fig. 4. A p-channel FET's main advantage in the high-side switch position lies in the simplified gate driving technique. Coupling the simpler gate driver with low  $R_{DS(ON)}$  performance increases system efficiency, reduces design complexity and decreases overall system cost. Additionally, p-channel FETs are ideal for point of loads or low-voltage drives in space-constrained systems.

In a load switching application, turning on an n-channel device requires that gate-voltage is greater than output voltage:

$$V_G \ge V_{OUT} + V_{th}$$

where  $V_G$  = gate-voltage,  $V_{th}$  = threshold voltage,  $V_{OUT}$  = output voltage and  $V_{IN}$  = input voltage.

This translates to requiring an additional biasing supply to achieve the higher gate-voltage.

In contrast, turning on a p-channel device requires input voltage to be greater than the threshold voltage:  $V_{IN} \ge V_G + V_{th}$  which is typically the case where  $V_{IN(minimum)} > 3.3$  V or 5 V. When gate is pulled low, the device is turned on and vice versa.

With this typically true for p-channel transistors, the advantage over n-channel FETs is clear: the simplicity of its gate-driver circuitry, and on/off control.

© 2023 How2Power. All rights reserved.

Fig. 4. Load switch circuit using p-channel MOSFETs.

There is a tradeoff consideration using n-channel vs. p-channel in this application. The benefit of using an nchannel device is its lower  $R_{DS(ON)}$  but it requires additional circuitry, a high-side driver. In older generation FETs, the SOA performance delta was not great enough to warrant use of a p-channel to avoid a complex gate driver design. However, with the robust SOA performance and significantly lower  $R_{DS(ON)}$  of latest generation pchannel devices, simplifying the gate driver translates into greater efficiency, board space savings, and lower system costs.

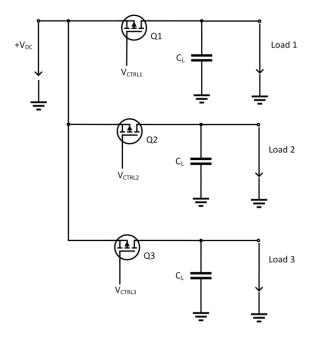

## Load Sequencing

Load sequencing is another application ideally suited to p-channel FETs. Today's satellites increasingly use more high-power FPGAs, ASICs, microcontrollers and DSPs for digital payload on-board processing. Such systems may have strict, specific load-sequencing requirements for optimal bus operation, reliability and other application needs.

Using n-channel FETs in low-voltage drive applications has similar design complexities. In this case, for turn-on, the gate driver for an n-channel high-side switch would need a bootstrap or a charge pump circuit to create a gate voltage greater than the isolated power supply or motor voltage rail. Again, this translates to more design effort and board space consumption. Using p-channel FETs in this application is again simpler. See Fig. 5.

### **Redundancy For Power Sources And Load**

Redundancy is another way to enhance spacecraft reliability. This is especially critical in a satellite distribution power architecture (DPA) to eliminate single points of failure. For example, there may be two intermediate bus converters (IBCs) connected to one load to provide redundancy of power source. There can also be two identical loads connected with a single power source to provide load redundancy. Such a system architecture allows continuity and prevents disruption of service.

Fig. 5. Simplified gate driving with p-channel versus n-channel MOSFETs.

## Inrush Current Limiting

A simplified schematic for an inrush current limiting circuit using a p-channel MOSFET is shown in Fig. 6. This is the same circuit shown in Fig. 2, but repeated here for convenience. For an example implementation, we refer to an evaluation board using IR HiRel's R9 rad hard p-channel FET in a low-ohmic TO-257AA package (Fig. 7). Designed to demonstrate the peak capability of an R9 superjunction p-channel in linear mode applications, the design is a load-switching circuit where a p-channel MOSFET controlled via another transistor (an n-channel device) can connect or disconnect the load from the bus.

Fig. 6. Typical implementation of Inrush current limiter.

The PCB is configured to have a 28-V input from a dc power supply. An external electronic load is connected to emulate the required steady-state load current. The main p-channel MOSFET (controlled via the n-channel control FET) is off in the initial state. When the control signal is applied to the control transistor, the p-channel MOSFET starts to turn on in a controlled manner and limits the inrush current. A controlled charging of a 400- $\mu$ F output capacitor takes place and then consequently the p-channel MOSFET fully turns-on (shown in Fig. 8 and Fig. 9) to conduct steady-state load current.

Fig. 7. Inrush current limiter evaluation board using the IRHYS9A97034CM.

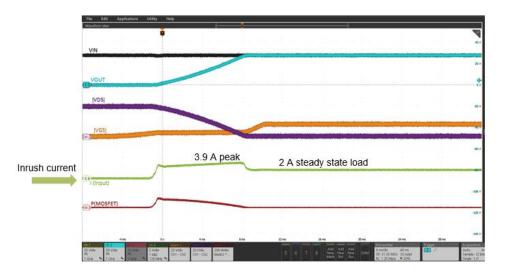

*Fig. 8. R5 SOA performance in the TO-257AA package limits use to <50-W converters in inrush current limiting applications.*

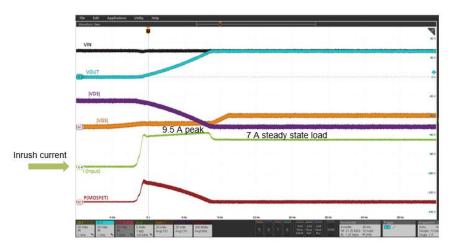

Fig. 9. R9 performance in the same package can support >100 W of power dissipation in inrush current limiting applications.

© 2023 How2Power. All rights reserved.

In Fig. 8, which shows an inrush current measurement for an R5 device, the linear-mode duration is about 5 to 6 ms. As shown earlier in Fig. 3, for the 10-ms R5 SOA curve at 28 V, the drain current is limited to about 3.75 A for a device in the TO-257AA package. The inrush current is about 3.75 A for a 2-A load. This means that the output load may be up to 50 W.

If the user expects an inrush current of more than 4 A, then the next option in the R5 generation of MOSFETs is a SupIR-SMD or a TO-254AA package which is approximately 70% to 95% larger in package area compared to the TO-257AA package used here. However, switching to an R9 device allows the MOSFET to support a higher drain current in the TO-257AA package.

Fig. 9 shows the waveform with IR HiRel's newest R9 MOSFET. The die size and package are the same as in Fig. 8. As shown before in the datasheet SOA comparison, this device can withstand 2.5x higher drain current in the same situation.

This is validated here on the application board where a 7-A load and a peak of 9.5-A inrush current is seen in the green trace. This means that the R9 device can easily support 3x higher output power than what was possible with R5 in the same package. The static dc current rating for the R9 device is also 67% higher than the R5 device, reflecting the higher current capability of the new device.

### Conclusion

The latest-generation rad-hard p-channel FETs deliver higher current capability and can support higher current in linear-mode applications due to their better SOA. This means that system designers can forego larger die sizes or packages and device paralleling, which sacrifices solution size and weight.

To enable easier implementation in application, the SOA of R9 p-channel MOSFETs is characterized at 25°C as well as at an 85°C case temperature. The R9 technology platform coupled with a low-ohmic TO-257AA package offers high current capability of 30 A with a footprint of 145 mm<sup>2</sup>.

Besides significant improvements in electrical switching performance, evidenced in their lower figure of merit, IR HiRel's R9 p-channel transistors have substantially improved electrical linear mode and single-event-effects (SEEs) safe operating area compared to the previous generation of R5 planar MOSFETs. The improvements in linear-mode safe operating area enables higher power density as well as higher reliability of power distribution circuits in space power systems.

#### Reference

- 1. Learn more at <u>www.infineon.com/supir-smd</u>.

- 2. Download the IRHYS9A97034CM datasheet.

### About The Authors

Oscar Mansilla is director of Discrete and IC Space Power Products for IR HiRel, where he leads development of new silicon and GaN-based FET solutions for the space industry. He can be reached at <u>oscar.mansilla@infineon.com</u>.

Rushi Patel is an applications engineer for IR HiRel and part of the technical marketing team. He can be reached at <u>rushi.patel@infineon.com</u>.

© 2023 How2Power. All rights reserved.

*Michelle Lozada leads digital marketing communications for IR HiRel. She can be reached at <u>michelle.lozada@infineon.com</u>.*

For more on MOSFET packaging, see How2Power's <u>Design Guide</u>, locate the "Design Area" category and select "Packaging And Interconnects". For more on space-grade power components and power converters in general, see How2Power's special section on <u>Space Power</u>.